RDA16110E-Fully Integrated Satellite receiver for DVB-S,DVB-S2,ABS-S,MMDS RF Point Pte Ltd

RDA Exclusive China Overseas Sales Agent

## **RDA16110E Programming Guide**

RDA Exclusive China Overseas Sales Agent

## **Change List**

| Rev | Date      | Author       | Change Description |

|-----|-----------|--------------|--------------------|

| 1.0 | 2011-8-31 | Hongxin Wang | Original draft     |

|     |           |              |                    |

|     |           |              |                    |

|     |           |              |                    |

|     |           |              |                    |

# RF POINT

## **RDA Microelectronics, Inc.**

## RDA16110E-Fully Integrated Satellite receiver for DVB-S,DVB-S2,ABS-S,MMDS RF Point Pte Ltd

RDA Exclusive China Overseas Sales Agent

#### 1. Introduction

RDA16110E enable software programming through I2C interface. Software controls chip working states, and allows user read status registers to get operation result through I2C interface.

#### 2. I2C Interface

The I2C interface of RDA16110E is compliant to I2C-Bus Specification 2.1(Fast-mode, bit rate up to 400Kbit/s). It includes two pins: SCLK and SDA. SCLK is an input pin; SDA is a bi-direction pin.

The I2C interface transfer begins with START condition, a command byte and data bytes, each byte has a followed ACK (or NACK) bit, and ends with STOP condition. The command byte includes a 7-bit device address  $\{5'b00011, MA1, MA0\}$  and an  $r/\overline{w}$  bit. (MA1 and MA0's values depends on input pin ADD's voltage, default 2'b00.) The ACK (or NACK) is always sent out by the receiver. When in write transfer process, data bytes are written out from MCU, and when in read transfer process, data bytes are read out from RDA16110E.

The RDA16110E contains status/control registers. These read/write registers are addressed as sub-address on the I2C bus. RDA16110E I2C interface supports both single and sequential register access. Software could follow the following ways to perform register read/write access:

## Random access single write

| Start | Device  | W | Α | Register A Register A stop |

|-------|---------|---|---|----------------------------|

|       | address |   |   | address data               |

## Random access sequential write

| Start | Device  | W | A Register | A | Register | A | Register | <br>Register | A | stop |

|-------|---------|---|------------|---|----------|---|----------|--------------|---|------|

|       | address |   | N address  |   | N Data   |   | N+1Data  | N+M Data     |   |      |

## Random access single read

| Start | Device  | W | A | Register | A | start | Device  | R | A | Register | N | stop |

|-------|---------|---|---|----------|---|-------|---------|---|---|----------|---|------|

|       | address |   |   | address  |   |       | address |   |   | Data     |   |      |

## Random access sequential read

| Ī | Start | Device  | W | A | Register | A | start | Device  | R | A | Register | Α | Register | A | <br>Register | N | stop |

|---|-------|---------|---|---|----------|---|-------|---------|---|---|----------|---|----------|---|--------------|---|------|

|   |       | address |   |   | N        |   |       | address |   |   | N        |   | N+1      |   | N+M          |   |      |

|   |       |         |   |   | address  |   |       |         |   |   | Data     |   | Data     |   | Data         |   |      |

W: Write Bit (0: write; 1: read)

A: Acknowledge Bit (ACK)

N: Not Acknowledge Bit (NO ACK)

## RDA16110E-Fully Integrated Satellite receiver for DVB-S,DVB-S2,ABS-S,MMDS RF Point Pte Ltd

RDA Exclusive China Overseas Sales Agent

For random access single write transfer, MCU sends out the START signal, RDA16110E's device address and 1 bit write signal in sequence to the I2C bus. After receiving RDA16110E's ACK signal, MCU sends out the target register's address (8 bits) to RDA16110E and then programs this register with proper data (8 bits). A STOP signal is sent out by MCU to end this transfer when programming is finished.

For random access sequential write transfer, MCU sends out the START signal, RDA16110E's device address and 1 bit write signal to the I2C bus. After receiving RDA16110E's ACK signal, MCU sends the sequential registers' first address (8 bits) to RDA16110E. Then MCU could program these registers sequentially. A STOP signal is sent out by MCU to end this transfer when programming is finished.

For random access single read transfer, MCU first sends out the START signal, the RDA16110E's device address and 1 bit write signal to the I2C bus. After receiving RDA16110E's ACK signal, MCU sends the target register's address (8 bits) to the interface. Then MCU should send another command byte, including a RESTART signal, the RDA16110E's device address and 1 bit read signal. Then RDA16110E will send the register's data to MCU through I2C bus. After the byte has been received, MCU should send a NO ACK response signal and a STOP signal to finish this read transfer.

For random access sequential write transfer, MCU first sends out the START signal, the RDA16110E's device address and 1 bit write signal to the I2C bus. After receiving RDA16110E's ACK signal, MCU sends the sequential registers' first address (8 bits) to RDA16110E. Then MCU should send another command byte to the interface, including a RESTART signal, the RDA16110E's device address and 1 bit read signal. Then RDA16110E starts to transfer the sequential registers' data byte by byte to MCU through I2C bus, each byte followed by an ACK response signal generated by the MCU. After all target registers' data have been read, MCU should send a NO ACK signal and a STOP signal to finish this read transfer.

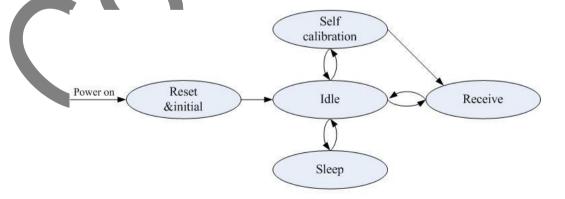

#### 3. States

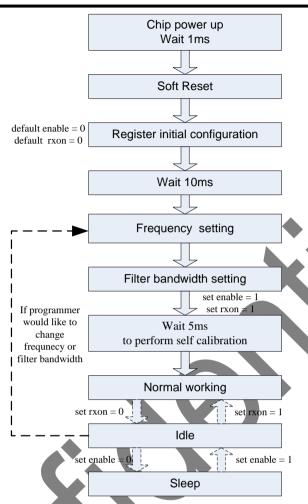

RDA16110E has five states: reset&initial, idle, self calibration, receive and sleep, as shown in Figure 1.

Figure 1 RDA16110E status

## RDA16110E-Fully Integrated Satellite receiver for DVB-S,DVB-S2,ABS-S,MMDS RF Point Pte Ltd

RDA Exclusive China Overseas Sales Agent

After chip power up, RDA16110E enters into reset&initial state automatically. Setting ENABLE (04h bit7) high and RXON bit (04h, bit1) high could bring RDA16110E enters into self calibration state to act corresponding calibration operation. If self calibration has been finished, RDA16110E will enter into receiving state (normal working state) automatically.

Software clears ENABLE bit could bring RDA16110E into sleep mode, all register contents are maintained. In sleep state, if software set ENABLE bit high, RDA16110E will enter back into normal working state.

When MCU wants to change receiving channel frequency, RXON bit should be cleared. MCU could write the frequency point value to the corresponding registers (07h, 08h, 09h and 0ah) and then set the RXON bit high.

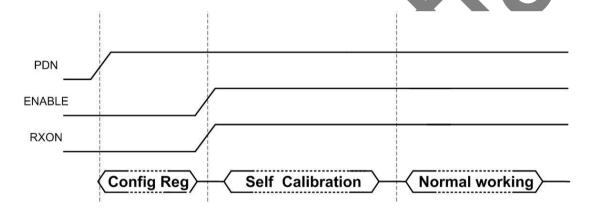

Figure 2 Normal work timing sequence

#### 4. Frequency Setting

When frequency is changed in reset&config state, software need program correct channel frequency. The frequency value format used in RDA16110E is a 30-bit binary format, put in register 07H [5:0], 08H[7:0], 09H[7:0] and 0aH[7:0]. Software need to translate the channel frequency into 30-bit binary format, and then write into RDA16110E.

Equation of 30-bit binary format and channel frequency: (f is frequency, {07H [5:0], 08H [7:0], 09H [7:0], 0aH [7:0]} is the 30-bit format frequency value, f\_xtal is the xtal frequency.)

$\{07H[5:0], 08H[7:0], 09H[7:0], 0aH[7:0]\} = dec2bin(f*(2^21)/f_xtal)$

## RDA16110E-Fully Integrated Satellite receiver for DVB-S,DVB-S2,ABS-S,MMDS RF Point Pte Ltd

RDA Exclusive China Overseas Sales Agent

For example: If the channel frequency is 950MHz, xtal frequency is 27M, translate the 950MHz into 30-bit binary format:

$dec2bin(950*(2^21)/27) = 30'b0000 0100 0110 0101 1110 1101 0000 1001$

software should program RDA16110E register 07H,08H,09H and 0AH using the follow programming sequence:

Mov 8'b0000\_0100(04), 07H Mov 8'b0110\_0101(65), 08H Mov 8'b1110\_1101(ed), 09H Mov 8'b0000 1001(09), 0aH

Attention: Frequency changing should always be done in reset&initial state or idle state. When chip in normal working state, programmer should write 1'b0 to rxon register (04h [1]) before setting new frequency value. After frequency setting has been finished, programmer could write 1 to rxon register (04h [1]), leading the chip into self calibration state and then into receiving state again.

### 5. Filter bandwidth setting

The filter bandwidth of RDA16110E is adjustable (from 4M to 40M, step 1M). Software could control RDA16110E's filter bandwidth by setting register 0bh[5:0]. For example, if the target bandwidth is 10MHz, software should program 0bh [5:0] to 6'd10; if the target bandwidth is 22MHz, software should program 0bh [5:0] to 6'd22, etc...

## 6. Register configuration sequence

Programmer should initialize and configure RDA16110E's register file following the sequence shown in Figure 3, and a detailed register configuration example is also provided in this section.

## RDA16110E-Fully Integrated Satellite receiver for DVB-S,DVB-S2,ABS-S,MMDS RF Point Pte Ltd

RDA Exclusive China Overseas Sales Agent

Figure 3 RDA5815 configuration sequence

## **Example I2C interface programming**

Supply power ready.

Toggle PDN pin from low to high.

PDN pin hold high.

Wait 1ms.

// Chip register soft reset

RDA16110eWriteReg(0x04,0x04);

RDA16110eWriteReg(0x04,0x05);

//pll setting

RDA16110eWriteReg(0x1a,0x13);

RDA16110eWriteReg(0x41,0x53);

RDA16110eWriteReg(0x38,0x93);

RDA16110eWriteReg(0x39,0x15);

### RDA16110E-Fully Integrated Satellite receiver for DVB-S,DVB-S2,ABS-S,MMDS RF Point Pte Ltd

RDA Exclusive China Overseas Sales Agent

RDA16110eWriteReg(0x3a,0x00); RDA16110eWriteReg(0x3b,0x00); RDA16110eWriteReg(0x3c,0x0c); RDA16110eWriteReg(0x0c,0xe2); RDA16110eWriteReg(0x2e,0x6f); RDA16110eWriteReg(0x72,0x07); RDA16110eWriteReg(0x73,0x20); RDA16110eWriteReg(0x74,0x72); RDA16110eWriteReg(0x75,0x06); RDA16110eWriteReg(0x76,0x40); RDA16110eWriteReg(0x77,0x89); RDA16110eWriteReg(0x79,0x04); RDA16110eWriteReg(0x7a,0xfa); RDA16110eWriteReg(0x7b,0x12); RDA16110eWriteReg(0x7c,0xf7); RDA16110eWriteReg(0x5b,0x20); RDA16110eWriteReg(0x2f,0x57); RDA16110eWriteReg(0x0d,0x70); RDA16110eWriteReg(0x16,0x03); RDA16110eWriteReg(0x18,0x4b) RDA16110eWriteReg(0x30,0xff); RDA16110eWriteReg(0x5c,0xff); RDA16110eWriteReg(0x6c,0xff); RDA16110eWriteReg(0x6e,0xff); RDA16110eWriteReg(0x65,0x00); RDA16110eWriteReg(0x70,0x3f); RDA16110eWriteReg(0x71,0x3f); RDA16110eWriteReg(0x53,0xa8); RDA16110eWriteReg(0x46,0x21); RDA16110eWriteReg(0x47,0x84); RDA16110eWriteReg(0x48,0x10); RDA16110eWriteReg(0x49,0x08); RDA16110eWriteReg(0x60,0x80); RDA16110eWriteReg(0x61,0x80); RDA16110eWriteReg(0x6a,0x08); RDA16110eWriteReg(0x6b,0x63); RDA16110eWriteReg(0x69,0xf8); RDA16110eWriteReg(0x57,0x64); RDA16110eWriteReg(0x05,0x88);

RDA16110eWriteReg(0x28,0xFF);

### RDA16110E-Fully Integrated Satellite receiver for DVB-S,DVB-S2,ABS-S,MMDS RF Point Pte Ltd

RDA Exclusive China Overseas Sales Agent

RDA16110eWriteReg(0x06,0xf8); RDA16110eWriteReg(0x15,0xae); RDA16110eWriteReg(0x4a,0x68); RDA16110eWriteReg(0x4b,0x78); //agc setting RDA16110eWriteReg(0x4f,0x40); RDA16110eWriteReg(0x5b,0x20); // for blocker RDA16110eWriteReg(0x16,0x0C);//stage setting RDA16110eWriteReg(0x18,0x0C); RDA16110eWriteReg(0x30,0x1C); RDA16110eWriteReg(0x5c,0x5C); RDA16110eWriteReg(0x6c,0x6C); RDA16110eWriteReg(0x6e,0xAC); RDA16110eWriteReg(0x1b,0xBC); RDA16110eWriteReg(0x1d,0xFC); RDA16110eWriteReg(0x1f,0xFC); RDA16110eWriteReg(0x21,0xFD); RDA16110eWriteReg(0x23,0xFF): RDA16110eWriteReg(0x25,0xFF); RDA16110eWriteReg(0x27,0xFF); RDA16110eWriteReg(0x29,0xFF); RDA16110eWriteReg(0xb3,0xFF); RDA16110eWriteReg(0xb5,0xFF); RDA16110eWriteReg(0x17,0xFC); RDA16110eWriteReg(0x19,0xFC); RDA16110eWriteReg(0x31,0xFC); RDA16110eWriteReg(0x5d,0xFC); RDA16110eWriteReg(0x6d,0xFC); RDA16110eWriteReg(0x6f,0xFC); RDA16110eWriteReg(0x1c,0xFC); RDA16110eWriteReg(0x1e,0xFC); RDA16110eWriteReg(0x20,0xFD); RDA16110eWriteReg(0x22,0xFE); RDA16110eWriteReg(0x24,0xFE); RDA16110eWriteReg(0x26,0xFF);

### RDA16110E-Fully Integrated Satellite receiver for DVB-S,DVB-S2,ABS-S,MMDS RF Point Pte Ltd

RDA Exclusive China Overseas Sales Agent

RDA16110eWriteReg(0x2a,0xFF); RDA16110eWriteReg(0xb4,0xFF); RDA16110eWriteReg(0xb6,0xFF); RDA16110eWriteReg(0xb7,0x10); //start RDA16110eWriteReg(0xb9,0x41); RDA16110eWriteReg(0xbb,0x42); RDA16110eWriteReg(0xbd,0x4F); RDA16110eWriteReg(0xbf,0x4E); RDA16110eWriteReg(0xc1,0x55); RDA16110eWriteReg(0xc3,0x56); RDA16110eWriteReg(0xc5,0x56); RDA16110eWriteReg(0xa3,0x54); RDA16110eWriteReg(0xa5,0x33); RDA16110eWriteReg(0xa7,0x29); RDA16110eWriteReg(0xa9,0x2b); RDA16110eWriteReg(0xab,0x31); RDA16110eWriteReg(0xad,0x5F); RDA16110eWriteReg(0xaf,0x8A); RDA16110eWriteReg(0xb1,0xB2); RDA16110eWriteReg(0xb8,0x41); RDA16110eWriteReg(0xba,0x6E); RDA16110eWriteReg(0xbc,0x6F); RDA16110eWriteReg(0xbe,0x7C); RDA16110eWriteReg(0xc0,0x7B); RDA16110eWriteReg(0xc2,0x81); RDA16110eWriteReg(0xc4,0x81); RDA16110eWriteReg(0xc6,0x7B); RDA16110eWriteReg(0xa4,0x85); RDA16110eWriteReg(0xa6,0x70); RDA16110eWriteReg(0xa8,0x6C); RDA16110eWriteReg(0xaa,0x47); RDA16110eWriteReg(0xac,0x5E); RDA16110eWriteReg(0xae,0x89); RDA16110eWriteReg(0xb0,0xB2); RDA16110eWriteReg(0xb2,0xDA); RDA16110eWriteReg(0x81,0x6E); //rise RDA16110eWriteReg(0x82,0xA0); RDA16110eWriteReg(0x83,0xB0);

### RDA16110E-Fully Integrated Satellite receiver for DVB-S,DVB-S2,ABS-S,MMDS RF Point Pte Ltd

RDA Exclusive China Overseas Sales Agent

```

RDA16110eWriteReg(0x84,0xA5);

RDA16110eWriteReg(0x85,0xB4);

RDA16110eWriteReg(0x86,0xC0);

RDA16110eWriteReg(0x87,0xB4);

RDA16110eWriteReg(0x88,0xBE);

RDA16110eWriteReg(0x89,0xB3);

RDA16110eWriteReg(0x8a,0xA8);

RDA16110eWriteReg(0x8b,0x7B);

RDA16110eWriteReg(0x8c,0x6E);

RDA16110eWriteReg(0x8d,0x99);

RDA16110eWriteReg(0x8e,0xC1);

RDA16110eWriteReg(0x8f,0xEA);

RDA16110eWriteReg(0x90,0x10);

//fall

RDA16110eWriteReg(0x91,0x07);

RDA16110eWriteReg(0x92,0x10);

RDA16110eWriteReg(0x93,0x10);

RDA16110eWriteReg(0x94,0x16);

RDA16110eWriteReg(0x95,0x17);

RDA16110eWriteReg(0x96,0x10);

RDA16110eWriteReg(0x97,0x20);

RDA16110eWriteReg(0x98,0x00)

RDA16110eWriteReg(0x99,0x00);

RDA16110eWriteReg(0x9a,0x00);

RDA16110eWriteReg(0x9b,0x33);

RDA16110eWriteReg(0x9c,0x42);

RDA16110eWriteReg(0x9d,0x6F);

RDA16110eWriteReg(0x9e,0x9A);

Wait 10ms;

// Initial configuration ready

(Attention: Initial configuration should be performed only once after chip power up or soft reset.)

8'b1110 0001(e1), 04H;// RXON = 0

Mov

8'b0000_0111(07), 07H; // Frequency setting (1600MHz for example)

Mov

8'b0110_1000(68), 08H;

Mov

8'b0100_1011(4b), 09H;

Mov

Mov

8'b1101_1010(da), 0aH;

8'b0000 1010(0a), 0bH; // Filter bandwidth setting (BW=10MHz for example)

Mov

Mov

8'b1110_0011(e3), 04H; // Pull up enable and rxon; AGC enable;

Wait

5ms;

```

The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of RDA.

### RDA16110E-Fully Integrated Satellite receiver for DVB-S,DVB-S2,ABS-S,MMDS RF Po

RDA Exclusive China Overseas Sales Agent

// Normal working start ... (Configuration all ready) // When programmer would like to change working frequency to 1700MHz and filter band width to 5M, the following command sequence should be performed: Mov 8'b1110 0001(e1), 04H; // RXON = 0, change normal working state to idle state 8'b0000\_0111(07), 07H; // Frequency setting (1700MH) Mov Mov 8'b1101 1110(de), 08H; Mov 8'b1101\_0000(d0), 09H; Mov 8'b1001\_1000(98), 0aH; 8'b0000\_0101(05), 0bH; // Filter bandwidth setting ( change BW to 5M Mov 8'b1110\_0011(e3), 04H; // Pull up enable and rxon; AGC enable; Wait 5ms;

### 7. Register summary

Register 00h Chip ID\_1 (read only)

// Enter normal working state again ... (Configuration all ready

| Bit | Name          | Function                          | Note      |

|-----|---------------|-----------------------------------|-----------|

| 7:0 | Chip_ID[11:4] | 5812 chip id Default 8'b0101_1000 | read only |

default: 8'b0101 1000

default: 8'b1100 0000

Register 01h Chip\_ID\_2 (read only)

| Bit | Name        |     | Function         | Note      |

|-----|-------------|-----|------------------|-----------|

| 7:4 | Chip_ID[3:  | :0] | Default: 4'b1100 | read only |

| 3:0 | Revision_II | D   | Default: 4'b0000 | read only |

Register 02h Device ID (read only) default: 8'b0000 1100

| Bit | Name               | Function                       | Note      |

|-----|--------------------|--------------------------------|-----------|

| 7   | Reversed           | 1'b0                           |           |

| 6:2 | Device_ID_fix[4:0] | Chip address Fixed             | read only |

|     |                    | Default 5'h0_0011              |           |

| 1   | MA1                | address 1 selected via pin ADD | read only |

|     |                    | configuration                  |           |

|     |                    | Default 0                      |           |

## RDA16110E-Fully Integrated Satellite receiver for DVB-S,DVB-S2,ABS-S,MMDS

RDA Exclusive China Overseas Sales Agent

| 0 | MA0 | address   | 1    | selected | via | pin | ADD | read only |  |

|---|-----|-----------|------|----------|-----|-----|-----|-----------|--|

|   |     | configura | tion |          |     |     |     |           |  |

|   |     | Default 0 |      |          |     |     |     |           |  |

#### Register 04h Config Control register

| ster 04h | Config Control register   | default: 8'b0000_0101                                      |      |

|----------|---------------------------|------------------------------------------------------------|------|

| Bit      | Name                      | Function                                                   | Note |

| 7        | enable                    | if 1,enable interface;                                     |      |

|          |                           | if 0,sleep mode, only bandgap,xtal and adr_encoder         |      |

|          |                           | module power on                                            |      |

|          |                           | Default: 1'b0                                              |      |

| 6        | Bypass_rxon_agc_enable    | Default: 1'b0                                              |      |

| 5        | rf_bypass_enable_b        | 0: power up                                                |      |

|          |                           | 1: power down                                              |      |

|          |                           | Default: 1'b0                                              |      |

|          |                           | The bypass buf functions at power-up of the chip by        |      |

|          |                           | default. If this function is not required, set this bit to |      |

|          |                           | logic '1', which will save about 6mA current.              |      |

| 4        | bypass_tuning_enable      | If set to 1,bypass tuning calibration when changing        |      |

|          |                           | the filter bandwdith;                                      |      |

|          |                           | Default: 1'b0                                              |      |

| 3        | bypass_rxon_dc_cal_enable | If set to 1, bypass de offset ealibration when each        |      |

|          |                           | time changing the working freq or the filter               |      |

|          |                           | bandwdith;                                                 |      |

|          |                           | Default: 1 b0                                              |      |

| 2        | agc_en_b                  | If 0,AGC enable;                                           |      |

|          |                           | If 1,disable AGC;                                          |      |

|          |                           | Default 1                                                  |      |

| 1        | rxon                      | If 1, in rxon mode                                         |      |

|          |                           | Default 0                                                  |      |

| 0        | Soft_resetn               | If 0, then reset all the register of chip                  |      |

|          |                           | Default 1                                                  |      |

#### Register 07h PLL frequency setting1 (950MHZ)

| ister 07l | PLL frequency setting1 (950MHZ) | default: 8'b0000_0100                        |      |

|-----------|---------------------------------|----------------------------------------------|------|

| Bit       | Name                            | Function                                     | Note |

| 7:0       |                                 | pll freq setting, from MSB to LSB:10 integer |      |

|           | Freq_synthesize_reg [31:24]     | bits,22 decimal                              |      |

|           |                                 | [7:2] interger bits                          |      |

## RDA16110E-Fully Integrated Satellite receiver for DVB-S,DVB-S2,ABS-S,MMDS RF Point Pte Ltd

RDA Exclusive China Overseas Sales Agent

| Regi | ster 08h | PLL frequency setting 2     | default: 8'b0110_0101                       |      |

|------|----------|-----------------------------|---------------------------------------------|------|

|      | Bit      | Name                        | Function                                    | Note |

|      | 7:6      | Freq_synthesize_reg [23:22] | [1:0] integer bits                          |      |

|      | 5:0      | Erag symthosiza rag [21:16] | pll freq setting , 22 decimal bits [21:16]. |      |

|      |          | Freq_synthesize_reg [21:16] | decimal bits[21:16].                        |      |

#### Register 09h PLL frequency setting 3

| defau | 14.0 1 | .111 | Λ 1 | 1101  |

|-------|--------|------|-----|-------|

| derau | itio i | )    | v   | 11111 |

| Bit | Name                       | Function                                  | Note |

|-----|----------------------------|-------------------------------------------|------|

| 7:0 | Freq_synthesize_reg [15:8] | pll freq setting , 22 decimal bits[15:8]. |      |

|     | 11eq_synthesize_leg [13.6] | decimal bits[15:8].                       |      |

#### Register 0ah PLL frequency setting 4

### default:8'b0000 1001

| Bit | Name                      | Function                                | Note |

|-----|---------------------------|-----------------------------------------|------|

| 7:0 | Freq_synthesize_reg [7:0] | pll freq setting, 22 decimal bits[7:0]. |      |

|     |                           | decimal bits[7:0].                      |      |

### Register 0bh filter bandwidth setting register

## default:8'b0000\_1010

| Bit | Name                        | Function                                                | Note |

|-----|-----------------------------|---------------------------------------------------------|------|

| 7   | filter_bw_control_bit_extra | Default 1'b0                                            |      |

|     |                             | when the filter bandwidth between 4M~8M,                |      |

|     |                             | we use this bit to make the BW precision to 0.5M.       |      |

|     |                             | eg: when BW=4M,we could set                             |      |

|     |                             | filter_bw_control_bit 6'b00_0100,and                    |      |

|     |                             | filter_bw_control_bit_add 1'b0;                         |      |

|     |                             | when BW 4.5M,we could set filter_bw_control_bit         |      |

|     |                             | 6'b00_0100,and filter_bw_control_bit_add 1'b1;          |      |

| 6   | filter_fc_bit_dr            | If 1, filter fc control bits using value direct decoded |      |

|     |                             | from filter_bw_control_bit;                             |      |

|     |                             | If 0, filter fc control bits using tuning calibration   |      |

|     |                             | result.                                                 |      |

|     |                             | default: 0                                              |      |

| 5:0 |                             | filter bandwidth setting(4MHz $\sim$ 40MHz)             |      |

|     | filter_bw_control_bit [5:0] | eg:if user need bandwdth 10M, set this register to      |      |

|     |                             | 6'b00_1010.                                             |      |

### RDA16110E-Fully Integrated Satellite receiver for DVB-S,DVB-S2,ABS-S,MMDS RF Point Pte L

RDA Exclusive China Overseas Sales Agent

#### **Disclaimer**

The information provided here is believed to be reliable; RDA Microelectronics assumes no reliability for inaccuracies and omissions. RDA Microelectronics assumes no reliability for the use of this information and all such information should entirely be at the user's own risk. Specifications described and contained here are subjected to change without notice on the purpose of improving the design and performance. All of this information described herein should not be implied or granted for any third party. RDA Microelectronics does not authorize or warrant any RDA products for use in the life support devices or systems.

Copyright@2006 RDA Microelectronics Inc. All rights reserved

For technical questions and additional information about RDA Microelectronics Inc.

Website: www.rdamicro.com Mailbox: info@rdamicro.com

RDA Microelectronics (Shanghai), Inc.

Tel: +86-21-50271098 Fax: +86-21-50271099 RDA Microelectronics (Beijing), Inc.

Tel: +86-10-62635360 Fax: +86-10-82612663