# DATA SHEET

## **RDA16110SW**

Fully Integrated Satellite Dual Receiver for DVB-S/S2 with RF switch integrated

## **RDA Microelectronics, Inc.**

## **Update History**

| Rev | Date       | Author | History Description                |

|-----|------------|--------|------------------------------------|

| 1.0 | 2013-12-12 |        | The primary datasheet              |

| 1.2 | 2014-02-25 |        | Pin definiation correction (pg 10) |

|     |            |        |                                    |

|     |            |        |                                    |

|     |            |        |                                    |

|     |            |        |                                    |

|     |            |        |                                    |

### **Features**

- Single-chip Two channels RF-to-baseband Satellite receiver

- RF switches integrated

- CMOS Fully integrated RF front end

- Low noise and wide dynamic range zero-IF receiver

- Input frequency range: 900 to 2200 MHz

- Input signal level: -80 to 0 dBm

- More than 80dB gain control range

- Fully integrated PLL (dividers, charge pump, phase & frequency detectors, loop filters, etc.)

- Integrated RX VCO

- Integrated baseband LPF with selectable cut-off frequency from 4MHz to 40MHz with 1MHz step

- Integrated LNA with RF AGC

- Integrated reference oscillator (27MHz is defult)

- I<sup>2</sup>C bus interface

- Automatic gain control

- 0.11 µm RF CMOS technology

- 3V to 3.6V operation

- 5×5 mm QFN40

## **Applications**

- Set-top boxes

- Digital video recorders

- Digital television

- Satellite PC-TV

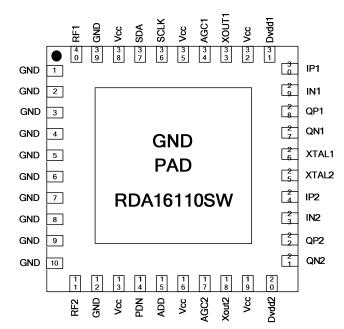

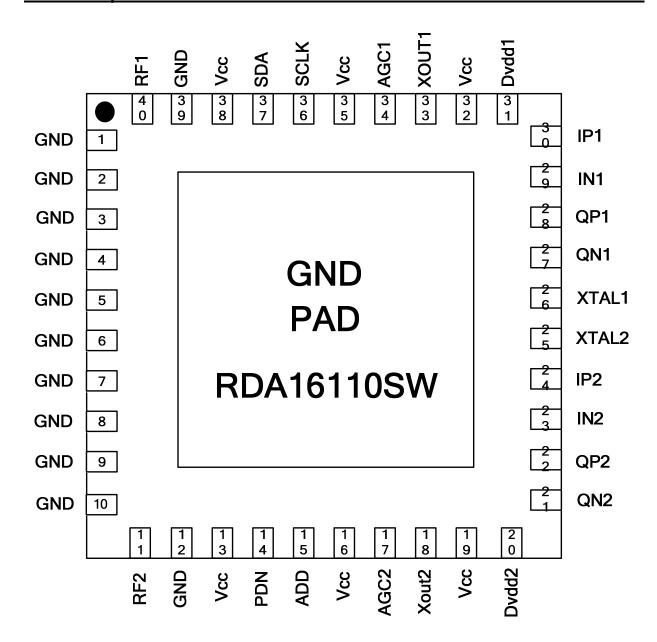

### Pin assignment (40 pin QFN 5×5 mm)

## **General Description**

The RDA16110SW is a two-channels fully integrated direct-convertion RF front end for DVB-S2 application.

There have two channels intergrated in RDA16110SW, each channel can be saperately controlled trough the I2C bus. With the RF switches, the two RF input signals can be switched between each other after setting the different switching modes.

The receiving frequency range is from 900MHz to 2200MHz, and the baseband filter's bandwidth can be selected from 4MHz to 40MHz with 1MHz step.

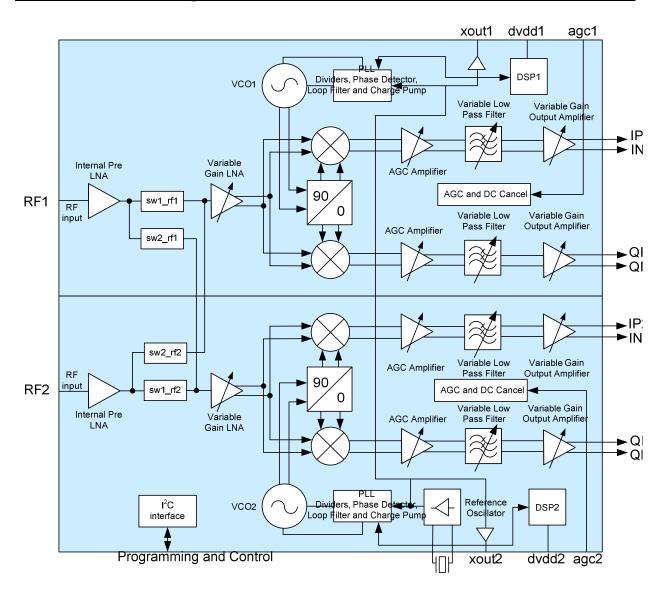

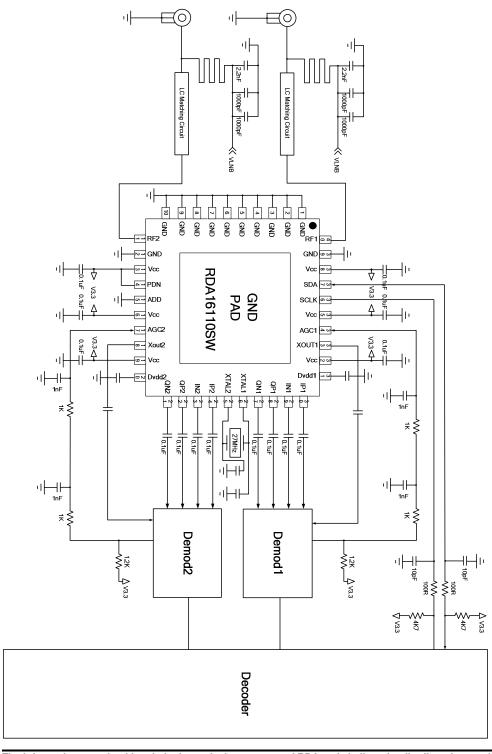

## **Functional Block Diagram**

# RDA Microelectronics, Inc. RDA16110SW- Fully Integrated Satellite DVB-S/S2 dual receiver

RF Point Pte Ltd

Exclusive RDA China Overseas Sales Agent

## **Function Descriptions**

As a dual-channel tuner product, RDA16110SW is made up of two individual RF cores in the silicon chip, only the Xtal clock and I2C bus are shared by the two channels. There are RF switches build at the front of variable gain LNA which enable receive of dual channel via dual RF inputs or any single RF Input. These RF switches are controlled via IIC bus.

Of each channel, there are two stages of LNA circuit in front of mixer – Internal Pre LNA and Variable Gain LNA. Variable Gain LNA is used to provide wide tuner dynamic range. Direct conversion architecture is used to convert the RF signal to in-phase and quadrature baseband signals. The signals which are required for direct conversion are all generated within the chip by fully integrated PLLs and quadrature LO generators. The frequency of the VCO is set by internal PLL circuits, which are programmable via a 2-wire (I²C) serial bus. The LO signals are mixed with the RF signal input and then filtered by low-pass filters to remove the upper image produced by the mixer. A variable gain amplifier is then used to adjust the baseband signal levels before processing by the channel selection filters to optimize noise performance and prevent distortion within the filters. The channel select filters are digital programmable low pass filters with 1MHz step from 4MHz to 40MHz. The output amplifier buffers the signal from the filters to increase the driving capability to the next baseband ADC.

Some innovative technique is used to correct and alleviate DC offsets inherent in direct conversion mixers, the channel select filters and output buffers.

#### LNA1&LNA2

LNA1 is the first LNA and receives signal from the LNB through external matching circuit, the input resistance is matched to  $75\,\Omega$  coaxial cable. The LNA2 is the second LNA and is used to provide wide dynamic range, the better noise figure. The gains of both LNA1 and LNA2 are programmable by the 2-wire ( $I^2C$ ) interface to insure wide dynamic range of the receiver.

#### **AGC Amplifier**

The AGC Amplifier receives the IQ signals from the quadrature mixer then amplifies them and sends to the base band low pass filter. The gain is also programmed and controlled by the 2-wire (I<sup>2</sup>C) interface.

#### **Baseband LPF**

The bansband low-pass filter is designed to have variable cut-off frequency. The bandwidth of the LPF is selectable from 4MHz to 40MHz with 1MHz step. The DC-offset calibration can be carried out controlled by the interface. Some innovative technique ensures the filter's bandwidth variety within 5%.

#### **Reference Oscillator**

The oscillator is on-chip integrated and both the crystal and crystal oscillator are supported. 27MHz is recommended.

# RDA Microelectronics, Inc. RDA16110SW- Fully Integrated Satellite DVB-S/S2 dual receiver

RF Point Pte Ltd

Exclusive RDA China Overseas Sales Agent

#### VCO

The receiver integrates two VCOs which ensure covering the full receiving frequency from 950MHz to 2150MHz. The VCO's bands are programmed using 2-wire (I<sup>2</sup>C) interface. VCO1 can work from 3700MHz to 6640MHz, and VCO2 can work from 5920MHz to 9080MHz. On each VCO band, some registers are configured differently between low section and high section, in order to keep better performance flatness. After being divided by four, LO signal from 950(3800/4) MHz to 2150(8600/4) MHz can be obtained.

| LO frequency                | Used VCO | Divider | Note                                                                |

|-----------------------------|----------|---------|---------------------------------------------------------------------|

| 950(3800/4)≤F≤1363(5452/4)  | VCO1     | 4       | VCO1 is used from 950 to 1579.  Between the bands of below 1363MHz  |

| 1364(5456/4)≤F≤1579(6316/4) | VCO1     | 4       | and upon 1364MHz, registers are fine-tuned differently.             |

| 1580(6320/4)≤F≤1862(7448/4) | VCO2     | 4       | VCO2 is used from 1580 to 2150.  Between the bands of below 1862MHz |

| 1863(7452/4)≤F≤2150(8600/4) | VCO2     | 4       | and upon 1863MHz, registers are fine-tuned differently.             |

#### **PLL**

The fractional-N frequency synthesizer use 27MHz reference as default. The dividers, loop filters, phase&frequency detector, charge pump are all integrated on chip.

#### **Baseband Output Amplifier**

Class-AB architecture is selected for the output buffer, this makes it more flexible to the next Baseband solution's input load. The gain of this stage can also be programmed with interface to farther increase the receiver dynamic.

#### I<sup>2</sup>C interface

The interface is the control unit of all the analog blocks, it is provided for configuration and monitoring all internal registers, the I<sup>2</sup>C bus consists of two wires: serial clock line (SCL) and serial data line (SDA). The LNA's gain, AGC, baseband LPF's bandwidth, VCO's and crystal oscillator's current, VCO's oscillation frequency are all controlled by the 2-wire interface.

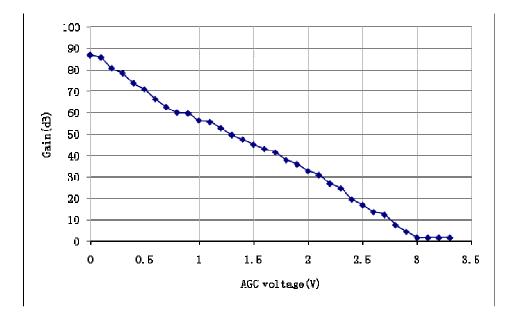

#### **Direct AGC control**

Through the AGC pin input, the receiver chain's gain can be directly controlled by the baseband solutions. The receiver gain changed inversely with the AGC control signal, this means that when AGC signal goes high, the receiver gain will drop to relevant level and vice versa.

## **Typical application circuit**

## **Pin Description**

# RDA Microelectronics, Inc. RDA16110SW- Fully Integrated Satellite DVB-S/S2 dual receiver

#### RF Point Pte Ltd

Exclusive RDA China Overseas Sales Agent

| Pin number | Name  | I/O | DESCRIPTION                                                                          |

|------------|-------|-----|--------------------------------------------------------------------------------------|

| 1~10,12,39 | GND   |     | Connected to Ground                                                                  |

| 11         | RF2   | 1   | The RF input pin for the channel 2                                                   |

| 13         | Vcc   | I   | Supply voltage for Channel 2, Connected to 3.3 V                                     |

| 14         | PDN   | I   | Chip power control                                                                   |

|            |       |     | If low, Receiver totally power down, including the crystal oscillator.               |

|            |       |     | If High, the chip is enabled.                                                        |

| 15         | ADD   | I   | I2C bus address selection terminal. Allowing the use of more than one device per I2C |

|            |       |     | bus system by the voltage on this pin.                                               |

|            |       |     | See Table 8 for programming details.                                                 |

| 16         | Vcc   | 1   | Supply voltage for Channel 2, Connected to 3.3 V                                     |

| 17         | AGC2  | 1   | AGC control input for the channel 2                                                  |

| 18         | Xout2 | 0   | Buffered Crystal oscillator output for demod2                                        |

| 19         | Vcc   | - 1 | Supply voltage for Channel 2, Connected to 3.3 V                                     |

| 20         | Dvcc2 | 0   | Output of the supply voltage for channel2's dsp, Connected to cap                    |

| 21         | QN2   | 0   | Negative Base-Band Q Channel2 Out                                                    |

| 22         | QP2   | 0   | Positive Base-Band Q Channel2 Out                                                    |

| 23         | IP2   | 0   | Positive Base-Band I Channel2 Out                                                    |

| 24         | IN2   | 0   | Negative Base-Band I Channel2 Out                                                    |

| 25         | Xtal2 | I/O | Connect to Crystal (27MHz is recommended)                                            |

| 26         | Xtal1 | I/O | Connect to Crystal (27MHz is recommended)                                            |

| 27         | QN1   | 0   | Negative Base-Band Q Channel1 Out                                                    |

| 28         | QP1   | 0   | Positive Base-Band Q Channel1 Out                                                    |

| 29         | IN1   | 0   | Positive Base-Band I Channel1 Out                                                    |

| 30         | IP1   | 0   | Negative Base-Band I Channel Out                                                     |

| 31         | Dvcc1 | 0   | Output of the supply voltage for channel1's DSP, Connected to cap                    |

| 32         | Vcc   | - 1 | Supply voltage for Channel 1, Connected to 3.3 V                                     |

| 33         | Xout1 | 0   | Buffered Crystal oscillator output for demod1                                        |

| 34         | AGC1  | 1   | AGC control input for the channel 1                                                  |

| 35         | Vcc   | 1   | Supply voltage for Channel 1, Connected to 3.3 V                                     |

| 36         | SCLK  | Į.  | Serial clock input                                                                   |

| 37         | SDA   | I/O | Serial data input/output, connected to 3.3V with 10kΩ resistor                       |

| 38         | Vcc   | 1   | Supply voltage for Channel 1, Connected to 3.3 V                                     |

| 40         | RF1   | I   | The RF input pin for the channel 2                                                   |

## **Electrical Specifications**

**Table 1** Recommended Operating Conditions

| Parameter             | Symbol         | MIN | TYP | MAX  | UNIT |

|-----------------------|----------------|-----|-----|------|------|

| Analog Supply Voltage | AVDD           | 3   | 3.3 | +3.6 | V    |

| Ambient Temperature   | T <sub>A</sub> | -25 | 27  | +85  | ~    |

## Table 2 DC Electrical Specification

| Parameter                     | Symbol          | MIN     | TYP     | MAX     | UNIT |

|-------------------------------|-----------------|---------|---------|---------|------|

| CMOS Low Level Input Voltage  | V <sub>IL</sub> | 0       |         | 0.3*VDD | V    |

| CMOS High Level Input Voltage | V <sub>IH</sub> | 0.7*VDD |         | VDD     | V    |

| CMOS Threshold Voltage        | $V_{TH}$        |         | 0.5*VDD |         | V    |

Table 3 Power consumption specification

(VDD =3 to 3.6 V,  $T_A$  = -25 to 85 °C, unless otherwise specified)

| Symbol | Description      | Condition        | TYP | UNIT |

|--------|------------------|------------------|-----|------|

| ICC    | Both Channels ON | Normal work      | 280 | mA   |

| ICC    | One Channel ON   | Normal work      | 145 | mA   |

| ICC    | Standby mode     | PDN = 1,Enable=0 | 6   | mA   |

| ICC    | Sleep mode       | PDN = 0          | 250 | uA   |

#### **Table 4** System Characteristics

(VDD = 3 to 3.6 V,  $T_A$  = -25 to 85 °C, unless otherwise specified)

| Parameter                    | SYMBOL          | CONDITIONS           | MIN | TYP | MAX  | UNIT |

|------------------------------|-----------------|----------------------|-----|-----|------|------|

| RF input frequency           | f <sub>IN</sub> |                      | 900 |     | 2200 | MHz  |

| Noise Figure                 | NF              | Max Gain             |     | 3.5 | 5    | dB   |

|                              |                 | (Minimum AGC)        |     |     |      |      |

| Input refered third-order    | IIP3            | Minimum Gain         | 9.5 | 10  | 11   | dBm  |

| intercept                    |                 | (Maximum AGC)        |     |     |      |      |

| Input refered econd-order    | IIP2            | Minimum Gain         |     | 60  |      | dBm  |

| intercept                    |                 | (Maximum AGC)        |     |     |      |      |

| Isolation of RF1 and RF2     |                 |                      | 36  | 45  | 60   | dB   |

| Gain flatness over           | GF              | Input freq=900 to    |     | 4   | 5    | dB   |

| frequency                    |                 | 2250MHz              |     |     |      |      |

| IQ amplitude balance         | IQAB            |                      |     |     | 0.5  | dB   |

| IQ phase balance             | IQPB            |                      |     |     | 0.5  | Deg  |

| Minimum voltage              | Gv(min)         | AGCIN set to maximum |     | -2  |      | dB   |

| conversion gain              |                 | (3.3 V)              |     |     |      |      |

| Maximum voltage              | Gv(max)         | AGCIN set to minimum |     | 85  |      | dB   |

| conversion gain              |                 | (0.1V)               |     |     |      |      |

| Voltage conversion gain      | Gv(step)        |                      |     | 0.2 |      | dB   |

| step                         |                 |                      |     |     |      |      |

| Matched input resistance     | R <sub>IN</sub> | After matching       |     | 75  |      | Ω    |

| Power up setting time        | PUST            |                      |     | 1   |      | ms   |

| Input reflection coefficient | S11             | After matching       |     | -10 |      | dB   |

#### **Table 5** Frequency Synthesizer Characteristics

(VDD = 3 to 3.6 V,  $T_A$  = -25 to 85 °C, unless otherwise specified)

| SYMBOL            | DESCRIPTION           | CONDITIONS | MIN  | TYP  | MAX  | UNIT   |

|-------------------|-----------------------|------------|------|------|------|--------|

| t <sub>sw</sub>   | RX Switch on time     |            |      | 200  |      | us     |

| f <sub>RFLO</sub> | synthesizer frequency |            | 900  |      | 2200 | MHz    |

| PN1               | Phase noise           | Δf=1kHz    |      | -88  | -80  | dBc/Hz |

| PN2               |                       | Δf=10kHz   | -100 | -95  | -90  | dBc/Hz |

| PN3               |                       | Δf=100kHz  | -110 | -105 | -100 | dBc/Hz |

| PN4               |                       | Δf=1MHz    | -138 | -133 | -130 | dBc/Hz |

## Table 6 Baseband LPF and Output Amplifier Characteristics

| Parameter                  | SYMBOL   | CONDITIONS     | MIN     | TYP     | MAX     | UNIT |

|----------------------------|----------|----------------|---------|---------|---------|------|

| 3 dB baseband filter       | BBF(3dB) |                | 4       |         | 40      | MHz  |

| bandwidth                  |          |                |         |         |         |      |

| Cutoff frequency accuracy  | FC       |                |         |         | +/-5    | %    |

| at -3dB                    |          |                |         |         |         |      |

| LPF 2fc attenuation        | LPF ATT1 |                | 25      |         |         | dB   |

| Flatness                   | FLTN     |                |         | 0.5     | 1       | dBpp |

| Group delay                | Td(g)    |                |         | 2       |         | ps   |

| Maximum differential       |          | Clipping level |         | 0.9*VDD |         | Vpp  |

| output voltage             |          |                |         |         |         |      |

| Output common mode         |          |                | 0.3*VDD | 0.5*VDD | 0.6*VDD | V    |

| voltage                    |          |                |         |         |         |      |

| Differential Output offset |          |                |         | 30      |         | mV   |

| voltage                    |          |                |         |         |         |      |

| IQ output impedance        |          |                | 25      | 45      | 55      | Ω    |

| Output Amplifier minimum   |          |                | 1K      |         |         | Ω    |

| load impedance             |          |                |         |         |         |      |

| Output Anplifier maximum   |          |                |         |         | 10      | pF   |

| Load capacitance           |          |                |         |         |         |      |

#### Table7 XTAL Characteristics

(VDD = 3 to 3.6 V,  $T_A$  = -25 to 85 °C, unless otherwise specified)

| Parameter                   | SYMBOL | MIN | TYP  | MAX | UNIT  |

|-----------------------------|--------|-----|------|-----|-------|

|                             | XTAL2  |     | 800  |     |       |

| Differential output voltage | XTAL1  |     | 810  |     | m\/nn |

| Differential output voltage | XOUT1  |     | 800  |     | mVpp  |

|                             | XOUT2  |     | 727  |     |       |

|                             | XTAL2  |     | 0.4  |     |       |

| Common mode voltage         | XTAL1  |     | 0.5  |     | V     |

| Common mode voltage         | XOUT1  |     | 0.81 |     | ľ     |

|                             | XOUT2  |     | 0.81 |     |       |

## Table 8 I<sup>2</sup>C Address selection

|                   | I2C Address |        |        |           |           |  |  |

|-------------------|-------------|--------|--------|-----------|-----------|--|--|

| ADD input voltage | bit<7:4>    | bit<3> | bit<2> | bit-      | <1>       |  |  |

|                   | 0001        | MA1    | MA0    | 0         | 1         |  |  |

| 0 V ~ 0.1 VDD     | 0001        | 0      | 0      | Channel_1 | Channel_2 |  |  |

| open              | 0001        | 0      | 1      | Channel_1 | Channel_2 |  |  |

| 0.9 VDD ~ VDD     | 0001        | 1      | 1      | Channel_1 | Channel_2 |  |  |

## Table 9 XOUT1&XOUT2 description

| XOUT_EN1(35pin) | XOUT1(33pin)                   |

|-----------------|--------------------------------|

| LOW             | No output                      |

| HIGH            | Output XTAL(crystal) frequency |

| XOUT_EN2(16pin) | XOUT2(18pin)                   |  |  |  |  |

|-----------------|--------------------------------|--|--|--|--|

| LOW             | No output                      |  |  |  |  |

| HIGH            | Output XTAL(crystal) frequency |  |  |  |  |

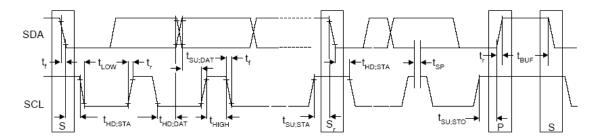

Table 10 I<sup>2</sup>C bus characteristics

(VDD = 3 to 3.6 V,  $T_A$  = -25 to 85 °C, unless otherwise specified)

| PARAMETER                          | SYMBOL                         | Test Condition | MIN | TYP | MAX | UNIT |

|------------------------------------|--------------------------------|----------------|-----|-----|-----|------|

| SCL Clock Frequency                | f <sub>SCL</sub>               |                | 0   |     | 400 | kHz  |

| Bus Free Time between START        |                                |                |     |     |     |      |

| and STOP Condition                 | $t_{BUF}$                      |                | 1.3 |     |     | μs   |

| Hold Time (repeated) START         |                                |                |     |     |     |      |

| Condition. (After this period, the |                                |                |     |     |     |      |

| first clock pulse is generated.)   | $T_{HD,STA}$                   |                | 0.6 |     |     | μs   |

| LOW Period of SCL Clock            | t <sub>LOW</sub>               |                | 1.3 |     |     | μs   |

| HIGH Period of SCL Clock           | t <sub>HIGH</sub>              |                | 0.6 |     |     | μs   |

| Data Setup Time                    | t <sub>SU,DAT</sub>            |                | 100 |     |     | ns   |

| Data Hold Time                     | t <sub>HD,DAT</sub>            |                | 0   |     | 0.9 | μs   |

| SCL and SDA Rise and Fall Time     | t <sub>f</sub> ,t <sub>f</sub> |                |     |     | 300 | ns   |

| Setup Time for a Repeated          |                                |                |     |     |     |      |

| START Condition                    | t <sub>SY,STA</sub>            |                | 0.6 |     |     | μs   |

| Setup Time for STOP Condition      | t <sub>SU,STO</sub>            |                | 0.6 |     |     | μs   |

| Capacitive Load for each Bus       |                                |                |     |     |     |      |

| Line                               | $C_B$                          |                |     |     | 400 | pF   |

I<sup>2</sup>C Timing Diagram

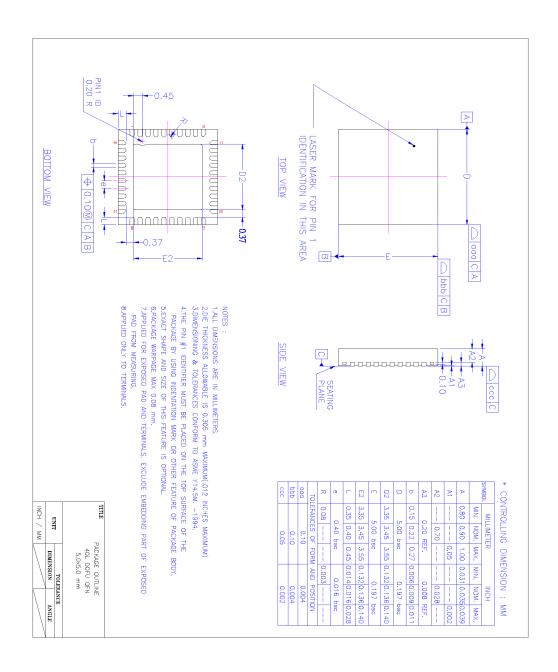

## **Package Outline**

40-Pin 5x5 Quad Flat No-Lead (QFN)

## **Solder Mounting Condition**

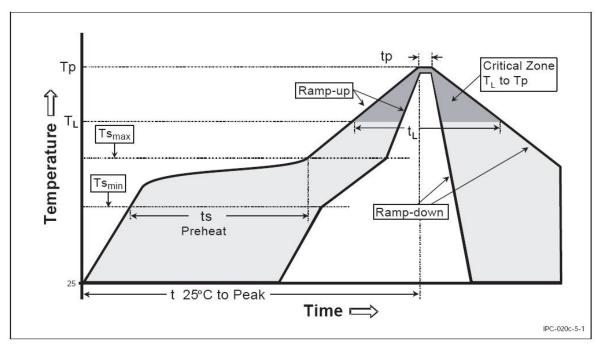

**Classification Reflow Profile**

RF Point Pte Ltd

#### Exclusive RDA China Overseas Sales Agent

#### **Table-I Classification Reflow Profiles**

| Profile Feature                                                  | Sn-Pb Eutectic Assembly | Pb-Free Assembly  |

|------------------------------------------------------------------|-------------------------|-------------------|

| Average Ramp-Up Rate (T <sub>Smax</sub> to T <sub>p</sub> )      | 3 °C/second max.        | 3 °C/second max.  |

| Preheat                                                          |                         |                   |

| -Temperature Min (T <sub>smin</sub> )                            | 100 °C                  | 150 °C            |

| -Temperature Max (T <sub>smax</sub> )                            | 100 °C                  | 200 °C            |

| -Time (t <sub>smin</sub> to t <sub>smax</sub> )                  | 60-120 seconds          | 60-180 seconds    |

| Time maintained above:                                           |                         |                   |

| -Temperature (T <sub>L</sub> )                                   | 183 °C                  | 217°C             |

| -Time (t <sub>L</sub> )                                          | 60-150seconds           | 60-150 seconds    |

| Peak /Classification<br>Temperature(T <sub>p</sub> )             | See Table-II            | See Table-III     |

| Time within 5 °C of actual<br>Peak Temperature (t <sub>p</sub> ) | 10-30 seconds           | 20-40 seconds     |

| Ramp-Down Rate                                                   | 6 °C/second max.        | 6 °C/seconds max. |

| Time 25 °C to Peak<br>Temperature                                | 6 minutes max.          | 8 minutes max.    |

## Table – II SnPb Eutectic Process – Package Peak Reflow Temperatures

| Package Thickness | Volume mm <sup>3</sup><br><350 | Volume mm³<br>≥350 |

|-------------------|--------------------------------|--------------------|

| <2.5mm            | 240 + 0/-5 ° C                 | 225 + 0/-5 ° C     |

| ≥2.5mm            | 225 + 0/-5 ° C                 | 225 + 0/-5 ° C     |

RF Point Pte Ltd

Exclusive RDA China Overseas Sales Agent

Table - III Pb-free Process - Package Classification Reflow Temperatures

| Package<br>Thickness | Volume mm <sup>3</sup> <350 | Volume mm <sup>3</sup><br>350-2000 | Volume mm <sup>3</sup> >2000 |

|----------------------|-----------------------------|------------------------------------|------------------------------|

| <1.6mm               | 260 + 0 ° C *               | 260 + 0 ° C *                      | 260 + 0 ° C *                |

| 1.6mm – 2.5mm        | 260 + 0 ° C *               | 250 + 0 ° C *                      | 245 + 0 ° C *                |

| ≥2.5mm               | 250 + 0 ° C *               | 245 + 0 ° C *                      | 245 + 0 ° C *                |

<sup>\*</sup>Tolerance : The device manufacturer/supplier **shall** assure process compatibility up to and including the stated classification temperature(this mean Peak reflow temperature + 0  $^{\circ}$  C. For example 260+ 0  $^{\circ}$  C ) at the rated MSL Level.

- Note 1: All temperature refer topside of the package. Measured on the package body surface.

- **Note 2:** The profiling tolerance is + 0 ° C, X ° C (based on machine variation capability)whatever is required to control the profile process but at no time will it exceed 5 ° C. The producer assures process compatibility at the peak reflow profile temperatures defined in Table –III.

- Note 3: Package volume excludes external terminals(balls, bumps, lands, leads) and/or non integral heat sinks.

- **Note 4:** The maximum component temperature reached during reflow depends on package the thickness and volume. The use of convection reflow processes reduces the thermal gradients between packages. However, thermal gradients due to differences in thermal mass of SMD package may sill exist.

- **Note 5:** Components intended for use in a "lead-free" assembly process **shall** be evaluated using the "lead free" classification temperatures and profiles defined in Table-I II III whether or not lead free.

Table 10 Junction Temperature specification

(VDD =3 to 3.6 V,  $T_A$  = -25 to 85 °C, unless otherwise specified)

| Symbol         | Description         | Condition                      |     | TYP   | MAX | UNIT        |

|----------------|---------------------|--------------------------------|-----|-------|-----|-------------|

| ΘјΑ            | Junction to Ambient |                                |     | 21.6  |     | %C\M        |

|                | Thermal Resistance  |                                |     |       |     |             |

| T <sub>j</sub> | Junction            | Ta (Ambient Temperature) -25 ℃ | -7  | -5.5  | -4  | $_{\infty}$ |

|                | Temperature         |                                |     |       |     |             |

| $T_j$          | Junction            | Ta (Ambient Temperature) 25 ℃  | 43  | 44.5  | 46  | $^{\circ}$  |

|                | Temperature         |                                |     |       |     |             |

| T <sub>j</sub> | Junction            | Ta (Ambient Temperature) 85 ℃  | 103 | 104.5 | 106 | $_{\infty}$ |

|                | Temperature         |                                |     |       |     |             |

Note:  $T_j = Ta + \Theta jA$  \* Power Consumption, MIN value comes from 3.0v VDD, TYP value comes from 3.3v VDD, MAX value comes from 3.6v VDD.

RF Point Pte Ltd

Exclusive RDA China Overseas Sales Agent

Table 11 Absolute Maximum ratings

| Symbol            | Description                   | MIN  | MAX | UNIT            |

|-------------------|-------------------------------|------|-----|-----------------|

| VDD               | Power supply voltage          | -0.3 | 3.6 | V               |

| T <sub>oper</sub> | Operating ambient Temperature | -25  | 85  | $_{\mathbb{C}}$ |

| Tj                | Junction Temperature          |      | 125 | ℃               |

## **RoHS Compliant**

The product does not contain lead, mercury, cadmium, hexavalent chromium, polybrominated biphenyls (PBB) or polybrominated diphenyl ethers (PBDE), and are therefore considered RoHS compliant.

## **ESD Sensitivity**

Integrated circuits are ESD sensitive and can be damaged by static electricity. Proper ESD techniques should be used when handling these devices.

## **RDA Microelectronics, Inc.** RDA16110SW- Fully Integrated Satellite DVB-S/S2 dual receiver

Exclusive RDA China Overseas Sales Agent

#### **Disclaimer**

The information provided here is believed to be reliable; RDA Microelectronics assumes no reliability for inaccuracies and omissions. RDA Microelectronics assumes no reliability for the use of this information and all such information should entirely be at the user's own risk. Specifications described and contained here are subjected to change without notice on the purpose of improving the design and performance. All of this information described herein should not be implied or granted for any third party. RDA Microelectronics does not authorize or warrant any RDA products for use in the life support devices or systems. Copyright@2005 RDA Microelectronics Inc. All rights reserved

For technical questions and additional information about RDA Microelectronics Inc.:

Website: www.rdamicro.com Mailbox: info@rdamicro.com

RDA Microelectronics (Beijing), Inc. RDA Microelectronics (Shanghai), Inc.

Tel: +86-21-50271108 Tel: +86-10-63635360 Fax: +86-10-82612663 Fax: +86-21-50271099

For Sales office: RF Point Pte Ltd 362 Upper Paya Lebar #04-10 Da Jin Factory Building Singapore 534963

Tel: +65-98636485

Mailbox:RF.Point@yahoo.com